Мультипроцесори

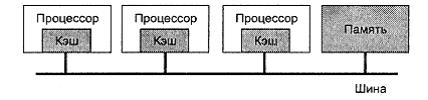

Мультипроцесорні системи володіють однією характерною особливістю: всі процесори мають прямий доступ до загальної пам'яті. Мультипроцесорні системи шинної архітектури складаються з деякої кількості процесорів, приєднаних до загальної шини, а через неї — до модулів пам'яті. Проста конфігурація містить плату з шиною або материнську плату, в яку вставляються процесори і модулі пам'яті.

Оскільки використовується єдина пам'ять, коли процесор A записує слово в пам'ять, а процесор В мікросекундою пізніше прочитує слово з пам'яті, процесор В отримує інформацію, записану в пам'ять процесором A. Пам'ять, що володіє такою поведінкою, називається узгодженою (coherent). Проблема такої схеми полягає в тому, що у випадку вже 4 або 5 процесорів шина виявляється стабільно переобтяженою і продуктивність різко падає. Рішення полягає в розміщенні між процесором і шиною високошвидкісної кеш-пам'яті (cache memory), як показано на рис.1. У кеші зберігаються дані, звернення до яких відбувається найчастіше. Всі запити до пам'яті відбуваються через кеш. Якщо запитані дані знаходяться в кеш-пам'яті, то на запит процесора реагує вона і звернення до шини не виконуються. Якщо розмір кеш-пам'яті достатньо великий, вірогідність успіху, звана також коефіцієнтом кеш-попаданій (hit rate), велика і шинний трафік з розрахунку на один процесор різко зменшується, дозволяючи включить в систему значно більше процесорів. Загальноприйнятими є розміри кеша від 512 Кбайт до 1 Мбайт, коефіцієнт кеш-попаданій при цьому зазвичай складає 90 % і більш.

Рис.1 Мультипроцесорна система з шинною архітектурою

Проте введення кеша створює серйозні проблеми саме по собі. Припустимо, що два процесори, A і В, читають одне і те ж слово в свій внутрішній кеш. Потім A перезаписує це слово. Коли процесор В наступного разу захоче скористатися цим словом, він рахує старе значення з свого кеша, а не нове значення, записане процесором A. Память стала неузгоджено, і програмування системи ускладнилося. Кешування проте активно використовується в розподілених системах, і тут ми знов стикаємося з проблемами неузгоджено пам'яті.

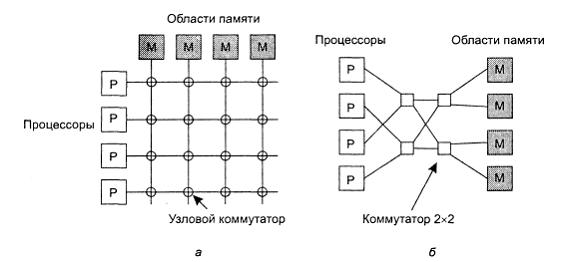

Проблема мультипроцесорних систем шинної архітектури полягає в їх обмеженій масштабованості, навіть у разі використання кеша. Для побудови мультипроцесорної системи з більш ніж 256 процесорами для з'єднання процесорів з пам'яттю необхідні інші методи. Один з варіантів — розділити загальну пам'ять на модулі і пов'язати їх з процесорами через комутуючі грати (crossbar switch), як показано на рис. 2, а. Як видно з малюнка, з її допомогою кожен процесор може бути пов'язаний з будь-яким модулем пам'яті. Кожен перетин є маленький електронний вузловий комутатор (crosspoint switch), який може відкриватися і закриватися апаратний. Коли процесор бажає дістати доступ до конкретного модуля пам'яті, що сполучають їх вузлові комутатори миттєво відкриваються, організовуючи запитаний доступ. Гідність вузлових комутаторів в тому, що до пам'яті можуть одночасно звертатися декілька процесорів, хоча якщо два процесори одночасно хочуть дістати доступ одній і тому ж ділянці пам'яті, то одному з них доведеться почекати.

Рис.2 Кумутаційна решітка (а), комутаційна омега-решітка

Недоліком комутуючих грат є те, що за наявності n процесорів і n модулів пам'яті нам буде потрібно n^2 вузлових комутаторів. Для великих значень n це число може перевищити наші можливості. Виявивши це, людство стало шукати і знайшло альтернативні комутуючі мережі, що вимагають меншої кількості комутаторів. Один з прикладів таких мереж — омега-мережа (omega network), представлена на мал. 2, б. Ця мережа містить чотири комутатори 2x2, тобто кожний з них має по два входи і два виходи. Кожен комутатор може сполучати будь-який вхід з будь-яким виходом. Якщо уважно вивчити можливі положення комутаторів, стає ясно, що будь-який процесор може дістати доступ до будь-якого блоку пам'яті. Недолік комутуючих мереж полягає в тому, що сигнал, що йде від процесора до пам'яті або назад, вимушений проходити через декілька комутаторів. Тому, щоб понизити затримки між процесором і пам'яттю, комутатори повинні мати дуже високу швидкодію, а дешевийоб це не дається.

Люди намагаються зменшити витрати на комутацію шляхом переходу до ієрархічних систем. В цьому випадку з кожним процесором асоціюється деяка область пам'яті. Кожен процесор може швидко дістати доступ до своєї області пам'яті. Доступ до іншої області пам'яті відбувається значно повільніше. Ця ідея була реалізована в машині з неуїіфіцированним доступом до пам'яті (Nonunifoim Memory Access, NUMA). Хоча машини NUMA мають кращий середній час доступу до пам'яті, чим машини на базі омега-сетей, у них є свої проблеми, пов'язані з тим, що розміщення програм і даних необхідно проводити так, щоб велика частина звернень йшла до локальної пам'яті.

Рис.2 Кумутаційна решітка (а), комутаційна омега-решітка

Недоліком комутуючих грат є те, що за наявності n процесорів і n модулів пам'яті нам буде потрібно n^2 вузлових комутаторів. Для великих значень n це число може перевищити наші можливості. Виявивши це, людство стало шукати і знайшло альтернативні комутуючі мережі, що вимагають меншої кількості комутаторів. Один з прикладів таких мереж — омега-мережа (omega network), представлена на мал. 2, б. Ця мережа містить чотири комутатори 2x2, тобто кожний з них має по два входи і два виходи. Кожен комутатор може сполучати будь-який вхід з будь-яким виходом. Якщо уважно вивчити можливі положення комутаторів, стає ясно, що будь-який процесор може дістати доступ до будь-якого блоку пам'яті. Недолік комутуючих мереж полягає в тому, що сигнал, що йде від процесора до пам'яті або назад, вимушений проходити через декілька комутаторів. Тому, щоб понизити затримки між процесором і пам'яттю, комутатори повинні мати дуже високу швидкодію, а дешевийоб це не дається.

Люди намагаються зменшити витрати на комутацію шляхом переходу до ієрархічних систем. В цьому випадку з кожним процесором асоціюється деяка область пам'яті. Кожен процесор може швидко дістати доступ до своєї області пам'яті. Доступ до іншої області пам'яті відбувається значно повільніше. Ця ідея була реалізована в машині з неуїіфіцированним доступом до пам'яті (Nonunifoim Memory Access, NUMA). Хоча машини NUMA мають кращий середній час доступу до пам'яті, чим машини на базі омега-сетей, у них є свої проблеми, пов'язані з тим, що розміщення програм і даних необхідно проводити так, щоб велика частина звернень йшла до локальної пам'яті.