Мікроархітектура процесорів. СПК

|

Зміст

Поняття мікроархітектури процесора

Під мікроархітектурою розуміється внутрішня реалізація програмної моделі.

Для однієї і тієї ж архітектури IA-32 різними фірмами і в різних поколіннях застосовуються істотно різні мікроархітектурні реалізації: при цьому, природно, прагнуть до максимального підвищення продуктивності (швидкості виконання програм). Починаючи з процесорів Р6 (і AMD К5), у мікроархітектурі застосовується RISC-ядро, що виконує мікрооперації (uOps), на які розкладаються складні інструкції х86. У результаті продуктивність процесора (за швидкістю виконання інструкцій х86) залежить від способу розкладання і швидкості виконання мікроінструкцій. При цьому підвищувати продуктивність можна різними способами: прискорювати виконання мікрооперацій (за рахунок підвищення тактової частоти), по можливості розпаралелити виконання мікрооперацій, скорочувати число мікрооперацій, необхідних для виконання однієї інструкції х86.

Аспекти мікроархітектури

Конвеєрний тракт даних є найбільш широко використовуваним в сучасних мікроархітектурах. Ця техніка використовується в більшості сучасних мікропроцесорів, мікроконтролерів і цифрових сигнальних процесорів. Конвеєрна архітектура дозволяє декільком інструкціям перекриватися у виконанні, що нагадує складальну лінію. Конвеєр включає кілька різних стадій, вибір яких є фундаментальним при розробці мікроархітектури. Деякі з цих стадій включають вибір інструкцій, декодування інструкцій, виконання і запис результату. Деякі архітектури включають інші стадії, такі як доступ до пам'яті. Дизайн конвеєра — один з центральних питань проектування мікроархітектури.

Пристрої виконання також є ключовими для мікроархітектури. Вони включають арифметико-логічні пристрої, пристрої обробки чисел з плаваючою комою, пристрої вибірки та зберігання, прогнозування розгалуження, паралелізм на рівні даних (SIMD). Ці блоки виробляють операції або обчислення процесора. Вибір числа блоків виконання, їх затримок, пропускної здатності та способу з'єднання пам'яті з системою також є мікроархітектурними рішеннями.

Проектні рішення рівня системи, такі як включати чи ні периферійні пристрої типу контролерів пам'яті, можуть вважатися частиною процесу розробки мікроархітектури, оскільки вони містять рішення за рівнем продуктивності і способам з'єднання цих периферійних пристроїв.

На відміну від архітектурного дизайну, де досягнення певного рівня продуктивності є головною метою, проектування мікроархітектури приділяє більшу увагу іншим обмеженням. Оскільки дизайн мікроархітектури прямо впливає на те, що відбувається в системі, увага повинна бути приділена наступним проблемам:

- Елемент маркованого списку

- Площа / вартість чипа

- Споживання енергії

- Складність логіки

- Простота з'єднань

- Технологічність

- Простота налагодження

- Тестованість.

Сучасні мікроархітектури процесорів

За останні роки сформувалося декілька напрямів або сімейств масових високопродуктивних мікропроцесорів, конкуруючих один з одним на ринку застосувань для десктопних комп'ютерів. Кожне сімейство має свою мікроархітектуру, або внутрішню організацію процесорного ядра, розроблену на основі уявлень її творців про потреби користувачів, критеріях оцінки продуктивності та інших споживчих якостей, перспективи розвитку та ринкових тенденціях. Ці уявлення впливають на прийняття розробниками принципових рішень про ті чи інші ключових архітектурні особливості процесора і про різні компроміси, закладених в архітектуру.

Мікроархітектура процесорів

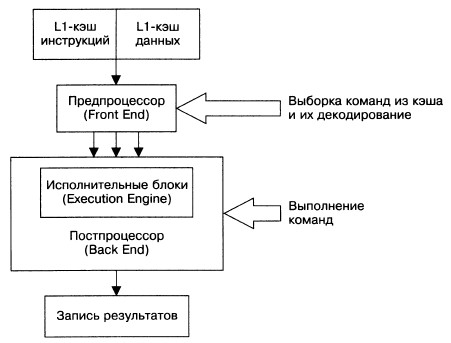

В основі архітектури будь-якого процесора лежить кілька конструктивних елементів : кеш команд і даних, предпроцессор ( Front End ) і постпроцесор, який називають також блоком виконання команд ( Execution Engine ).

Процес обробки даних складається з декількох характерних етапів. Насамперед інструкції і дані забираються з кеша L1 ( який розділений на кеш інструкцій і кеш даних). Ця процедура називається вибіркою. Після цього вибрані з кешу інструкції декодуються в зрозумілі для даного процесора примітиви ( машинні команди). Дана процедура називається декодуванням. Далі декодовані команди надходять на виконавчі блоки процесора, виконуються, а результат записується в оперативну пам'ять.

Процеси вибірки інструкцій з кеша, їх декодування і просування до виконавчих блокам здійснюються в предпроцесорі , а процес виконання декодованих команд - в постпроцесорі . Таким чином , навіть у самому простому випадку команда проходить як мінімум чотири стадії обробки :

- Вибірка з кеша;

- Декодування;

- Виконання;

- Запис результатів.

Дані стадії прийнято називати конвеєром обробки команд. У нашому випадку конвеєр є чотириступінчатим . Важливо, що кожну з цих щаблів команда повинна проходити рівно за один такт. Відповідно для чотириступінчастого конвеєра на виконання однієї команди відводиться рівно чотири такту.