Відмінності між версіями «Синхронна пам'ять SDRAM. СПК»

Матеріал з Вікі ЦДУ

Fomenko (обговорення • внесок) |

Fomenko (обговорення • внесок) |

||

| Рядок 7: | Рядок 7: | ||

== Команди, виконувані мікросхемою SDRAM == | == Команди, виконувані мікросхемою SDRAM == | ||

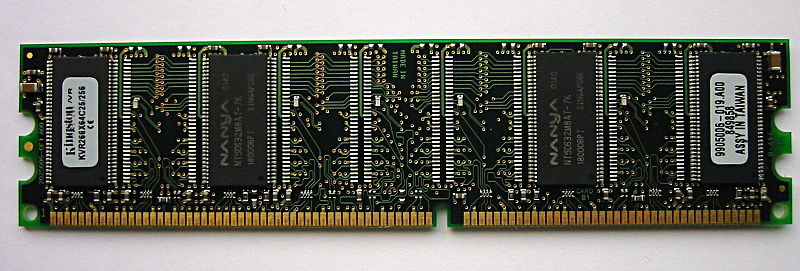

| − | + | [[Файл:DDR-SDRAM DIMM.jpg]] | |

# Встановлення регістра режимів | # Встановлення регістра режимів | ||

# Вхід в режим саморегенерації | # Вхід в режим саморегенерації | ||

Версія за 22:07, 19 листопада 2013

|

SDRAM - синхронна динамічна пам'ять з довільним доступом.

На відміну від інших типів DRAM, відповідь на команду повертається не відразу, а лише при отриманні тактового сигналу. Тактові сигнали дозволяють організувати роботу SDRAM у вигляді кінцевого автомата.

Пристрої SDRAM розділені на 2 або 4 незалежних банки пам'яті. Входи адреси першого і другого банку пам'яті ( BA0 і BA1 ) визначають, якому банку буде призначена поточна команда.

Команди, виконувані мікросхемою SDRAM

- Встановлення регістра режимів

- Вхід в режим саморегенерації

- Вихід з режиму саморегенерації

- Підзаряд як одного, так і всіх банків пам'яті

- Авторегенерація (CBR)

- Активація банку

- Запис та запис з автопідзарядом

- Читання та читання з автопідзарядом

- Завершення пакета

- Вхід та вихід з режиму призупинення синхронізації

- Запис / включення виходу

- Маска / виключення виходу

- Вхід та вихід з режиму зниженого енергоспоживання

Принцип дії

Команди подаються на контакти модуля по семи сигнальних лініях. По одній з них подається тактовий сигнал, передні фронти якого задають моменти часу, в котрі зчитуються команди управління з інших 6 командних ліній:

- CKE ( clock enable ) - при низькому рівні сигналу блокується подача тактового сигналу на мікросхему. Команди не обробляються, а стан інших командних ліній ігнорується.

- /CS ( chip select ) - при високому рівні сигналу всі інші керуючі лінії, крім CKE, ігноруються. Діє як команда NOP ( немає оператора).

- DQM ( data mask ) - забороняє читання / запис даних. При одночасно поданої команді запису дані не записуються в DRAM. Присутність цього сигналу в двох тактах, що передують циклу читання призводить до того, що дані не зчитуються з пам'яті.

- /RAS ( row address strobe ) - це всього лише один командний біт. Разом з /CAS і /WE кодує одну з 8 команд.

- /CAS ( column address strobe ) - це всього лише один командний біт. Разом з /RAS і /WE кодує одну з 8 команд.

- /WE ( write enable ) - Разом з /RAS і /CAS кодує одну з 8 команд.